野球ゲームをつくる ~ 12.野球ゲームの完成

これまで、モジュールを作成してきましたが、つなぎあわして野球ゲームを完成させます。

まず、ボードのInput/Outputをおさらいします。

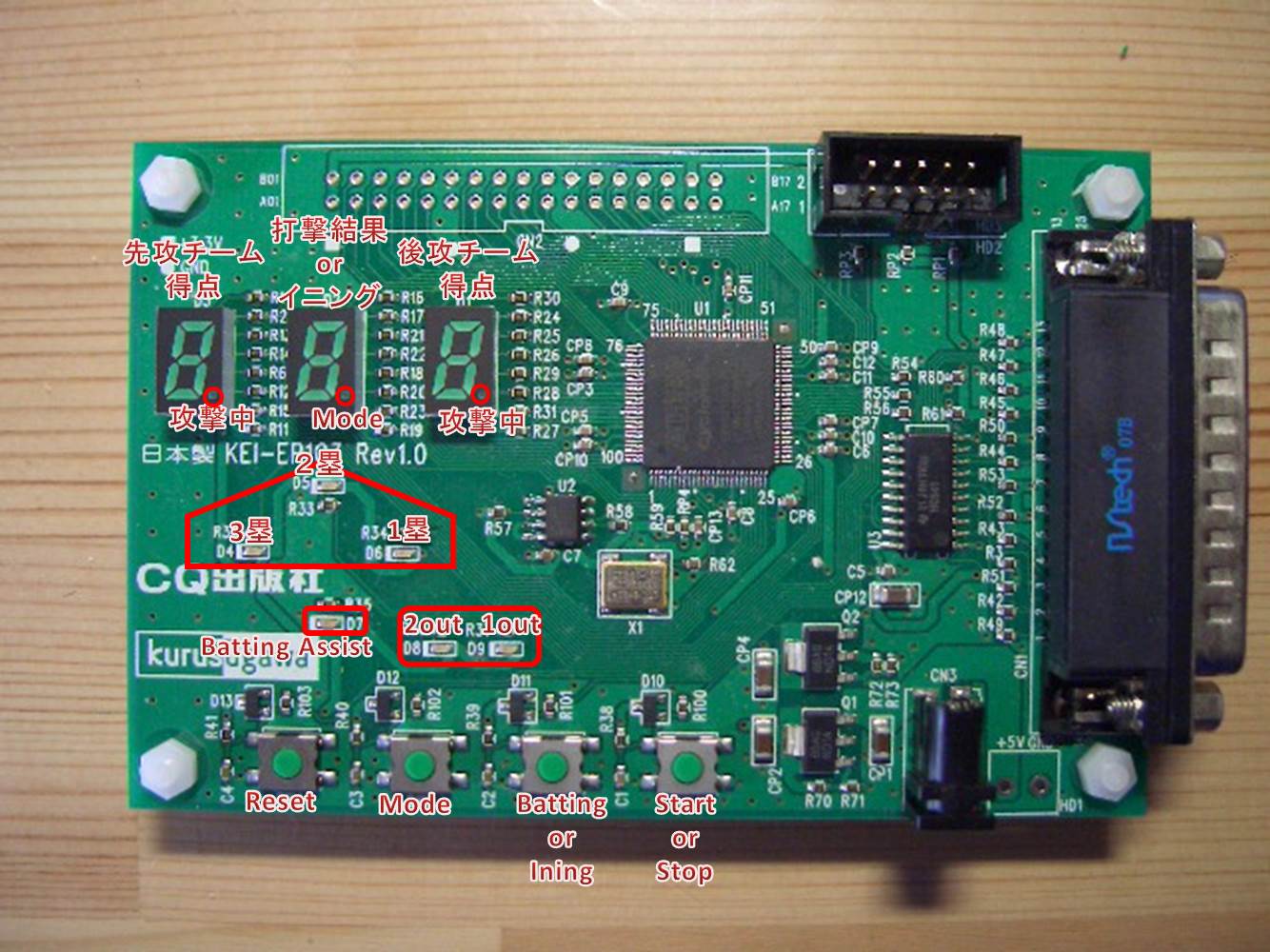

野球ゲームをつくる ~ 1.仕様の作成 にある仕様を元にボードの配置は下図のとおりです。

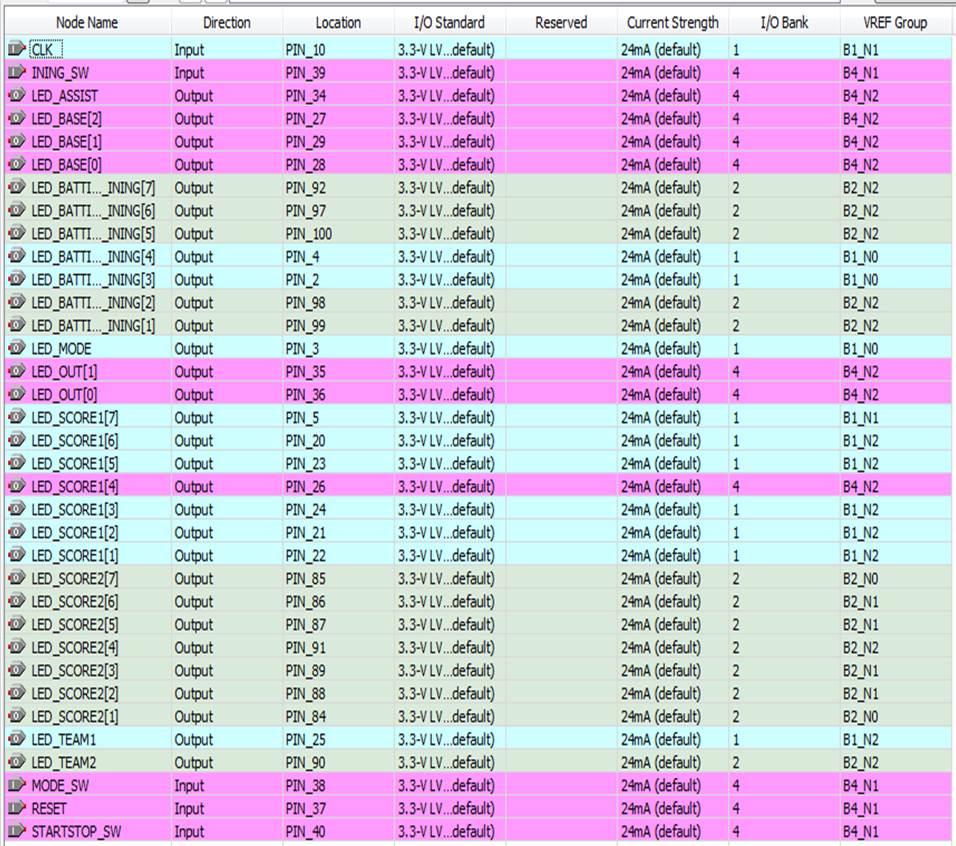

ピン配置は下図です。

回路図(RTL)は下図です。

-- BASEBALL GAME TOP Entity

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity BASEBALL_GAME is

port(

CLK : in std_logic;

RESET : in std_logic;

STARTSTOP_SW: in std_logic;

INING_SW : in std_logic;

MODE_SW : in std_logic;

LED_TEAM1 : out std_logic;

LED_TEAM2 : out std_logic;

LED_ASSIST : out std_logic;

LED_MODE : out std_logic;

LED_BASE : out std_logic_vector(2 downto 0);

LED_OUT : out std_logic_vector(1 downto 0);

LED_SCORE1 : out std_logic_vector(7 downto 1);

LED_SCORE2 : out std_logic_vector(7 downto 1);

LED_BATTING_OR_INING : out std_logic_vector(7 downto 1)

);

end BASEBALL_GAME;

architecture RTL of BASEBALL_GAME is

component DIVIDER

port(

CLK : in std_logic;

RESET : in std_logic;

DIV_CLK_2HZ : out std_logic;

DIV_CLK_8Hz : out std_logic;

DIV_CLK_16Hz: out std_logic;

DIV_CLK_32HZ: out std_logic

);

end component;

component CHATTERING_CUT

port(

SW : in std_logic;

CLK : in std_logic;

RESET: in std_logic;

COUT : out std_logic

);

end component;

component TOGLE

port(

TIN : in std_logic;

RESET : in std_logic;

TOUT : out std_logic

);

end component;

component BATTING_ROULLET

port(

CLK : in std_logic;

RESET : in std_logic;

STARTSTOP: in std_logic;

MODE : in std_logic;

BATTING : out std_logic_vector(2 downto 0);

ASSIST : out std_logic

);

end component;

component BASE

port(

CLK : in std_logic;

RESET : in std_logic;

SELECTOR: in std_logic;

CHANGE : in std_logic;

BATTING : in std_logic_vector(2 downto 0);

RUNNER : out std_logic_vector(2 downto 0);

SCORE1 : out std_logic_vector(3 downto 0);

SCORE2 : out std_logic_vector(3 downto 0);

TEAM1 : out std_logic;

TEAM2 : out std_logic;

BLINK : out std_logic

);

end component;

component BLINK

port(

CLK : in std_logic;

ENABLE: in std_logic;

BLINK : out std_logic

);

end component;

component OUT_COUNTER

port(

CLK : in std_logic;

RESET : in std_logic;

BATTING : in std_logic_vector(2 downto 0);

OUT_LED : out std_logic_vector(1 downto 0);

CHANGE : out std_logic

);

end component;

component INING_COUNTER

port(

CLK : in std_logic;

RESET : in std_logic;

COUNT : out std_logic_vector(3 downto 0)

);

end component;

component LUCKY7

port(

RESET : in std_logic;

INING_COUNT : in std_logic_vector(3 downto 0);

LED_ASSIST : out std_logic

);

end component;

component BATTING_DECODER

port(

RESET : in std_logic;

COUNTER : in std_logic_vector(2 downto 0);

LED : out std_logic_vector(7 downto 1)

);

end component;

component SCORE_DECODER

port(

DIV_CLK : in std_logic;

ENABLE : in std_logic;

RESET : in std_logic;

COUNTER : in std_logic_vector(3 downto 0);

LED : out std_logic_vector(7 downto 1)

);

end component;

component INING_DECODER

port(

RESET : in std_logic;

COUNTER : in std_logic_vector(3 downto 0);

LED : out std_logic_vector(7 downto 1)

);

end component;

signal CLK2HZ : std_logic;

signal CLK8HZ : std_logic;

signal CLK16HZ : std_logic;

signal CLK32HZ : std_logic;

signal STARTSTOP_CUT : std_logic;

signal MODE_CUT : std_logic;

signal STARTSTOP_TMP : std_logic;

signal MODE_TMP : std_logic;

signal BATTING_TMP : std_logic_vector(2 downto 0);

signal SCORE1_TMP : std_logic_vector(3 downto 0);

signal SCORE2_TMP : std_logic_vector(3 downto 0);

signal CHANGE_TMP : std_logic;

signal TOGLE_TEAM_TMP : std_logic;

signal RESET_OR_CHANGE : std_logic;

signal SELECT1_TMP : std_logic;

signal SELECT2_TMP : std_logic;

signal INING_COUNT_TMP : std_logic_vector(3 downto 0);

signal INING_LED_OUT : std_logic_vector(7 downto 1);

signal BATTING_LED_OUT : std_logic_vector(7 downto 1);

signal BATTING_ASSIST : std_logic;

signal LUCKY7_ASSIST : std_logic;

signal BLINK_CLK : std_logic;

signal BLINK_ENABLE : std_logic;

signal BLINK_TMP : std_logic;

begin

RESET_OR_CHANGE <= RESET and CHANGE_TMP;

SELECT1_TMP <= not TOGLE_TEAM_TMP;

SELECT2_TMP <= TOGLE_TEAM_TMP;

BLINK_ENABLE <= BLINK_TMP and not STARTSTOP_TMP;

LED_ASSIST <= not (BATTING_ASSIST and LUCKY7_ASSIST);

process(INING_SW,INING_LED_OUT,BATTING_LED_OUT)

begin

if (INING_SW = '0') then

LED_BATTING_OR_INING <= INING_LED_OUT;

else

LED_BATTING_OR_INING <= BATTING_LED_OUT;

end if;

end process;

process(RESET,MODE_TMP)

begin

if (RESET = '0') then

LED_MODE <= '1';

elsif (MODE_TMP = '1') then

LED_MODE <= '0';

else

LED_MODE <= '1';

end if;

end process;

CLK_DIVIDER :DIVIDER port map (CLK,RESET,open,CLK8HZ,open,CLK32HZ);

STARTSTOP_CT:CHATTERING_CUT port map (STARTSTOP_SW,CLK,RESET,STARTSTOP_CUT);

MODE_CT :CHATTERING_CUT port map (MODE_SW,CLK,RESET,MODE_CUT);

STARTSTOP_T :TOGLE port map (STARTSTOP_CUT,RESET,STARTSTOP_TMP);

MODE_T :TOGLE port map (MODE_CUT,RESET,MODE_TMP);

INING_T :TOGLE port map (CHANGE_TMP,RESET,TOGLE_TEAM_TMP);

ROULLET_UNIT:BATTING_ROULLET port map (CLK32HZ,RESET_OR_CHANGE,STARTSTOP_TMP,MODE_TMP,BATTING_TMP,BATTING_ASSIST);

BASE_UNIT :BASE port map (STARTSTOP_TMP,RESET,TOGLE_TEAM_TMP,CHANGE_TMP,BATTING_TMP,LED_BASE,SCORE1_TMP,SCORE2_TMP,LED_TEAM1,LED_TEAM2,BLINK_TMP);

BLINK_UNIT :BLINK port map (CLK8Hz,BLINK_ENABLE,BLINK_CLK);

LUCKY7_UNIT :LUCKY7 port map (RESET,INING_COUNT_TMP,LUCKY7_ASSIST);

COUNTER1 :OUT_COUNTER port map (STARTSTOP_TMP,RESET_OR_CHANGE,BATTING_TMP,LED_OUT,CHANGE_TMP);

COUNTER2 :INING_COUNTER port map (TOGLE_TEAM_TMP,RESET,INING_COUNT_TMP);

DECORDER1 :BATTING_DECODER port map (RESET,BATTING_TMP,BATTING_LED_OUT);

DECORDER2 :SCORE_DECODER port map (BLINK_CLK,SELECT1_TMP,RESET,SCORE1_TMP,LED_SCORE1);

DECORDER3 :SCORE_DECODER port map (BLINK_CLK,SELECT2_TMP,RESET,SCORE2_TMP,LED_SCORE2);

DECORDER4 :INING_DECODER port map (RESET,INING_COUNT_TMP,INING_LED_OUT);

end RTL;