ルーレットを止めます。

一旦止まるとリセットが入るまで、動きません。(動いたらルーレットじゃないですね)

-- oneshot

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity ONESHOT is

port(

RESET : in std_logic;

SW : in std_logic;

STOP_OUT: out std_logic -- ストップしているかどうか

);

end ONESHOT;

architecture RTL of ONESHOT is

begin

process(RESET,SW)

begin

if (RESET = '0') then

STOP_OUT <= '0';

elsif (SW'event and SW = '0') then

STOP_OUT <= '1';

end if;

end process;

end RTL;

SW'event and SW = '0' で一度STOP_OUT <= '1'になると、

リセットがかかるまで、STOP_OUT <= '0'になりません。

つまり、ルーレットは止まったままになります。

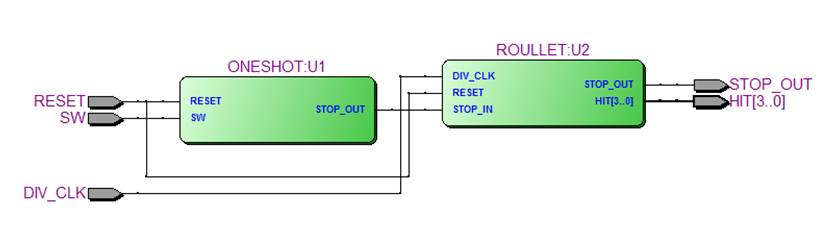

oneshot.vhd とroullet.vhd を組み合わせて、

slot.vhd にします。

-- slot

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity SLOT is

port(

DIV_CLK : in std_logic;

RESET : in std_logic;

SW : in std_logic;

STOP_OUT: out std_logic;

HIT : out std_logic_vector(3 downto 0)

);

end SLOT;

architecture RTL of SLOT is

component ONESHOT

port(

RESET : in std_logic;

SW : in std_logic;

STOP_OUT: out std_logic

);

end component;

component ROULLET

port(

DIV_CLK : in std_logic;

RESET : in std_logic;

STOP_IN : in std_logic;

STOP_OUT: out std_logic;

HIT : out std_logic_vector(3 downto 0)

);

end component;

signal STOP_TMP : std_logic;

begin

U1 :ONESHOT port map(RESET,SW,STOP_TMP);

U2 :ROULLET port map (DIV_CLK,RESET,STOP_TMP,STOP_OUT,HIT);

end RTL;