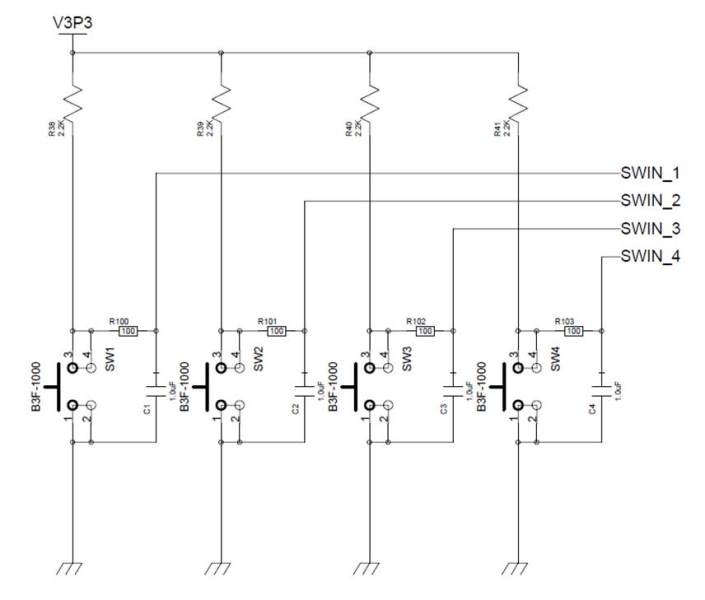

「改訂版 FPGAボードで学ぶ論理回路設計」の付属基盤は、チャタリング防止回路(RC回路)がありますが、

ソフト的にチャタリングを防止してみます。

簡単な方法は、チャタリングがおさまる時間以上のクロックでサンプリングすれば良いのですが、

サンプリングは10ms前後でいいようです。

そこで、33MHz -> 約64Hz 15.625ms の分周をつくってみます。

非同期リセットも入れてます。

負論理です。

-- Chattering CUT rate about 64Hz 15.625ms

-- InPutClock 33MHz

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity CHATTERING_CUT is

port(

SW : in std_logic;

CLK : in std_logic;

RESET: in std_logic;

COUT : out std_logic

);

end CHATTERING_CUT;

architecture RTL of CHATTERING_CUT is

signal DIV_COUNTER : std_logic_vector(24 downto 0);

signal DIV_CLK_64HZ : std_logic;

begin

process(CLK,RESET)

begin

if (RESET = '0') then

DIV_COUNTER <= (others => '0');

elsif (CLK'event and CLK = '0') then

DIV_COUNTER <= DIV_COUNTER + 1;

end if;

end process;

DIV_CLK_64HZ <= not DIV_COUNTER(18);

process(DIV_CLK_64HZ)

begin

if (DIV_CLK_64HZ'event and DIV_CLK_64HZ ='0') then

COUT <= SW;

end if;

end process;

end RTL;